プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 米国 DesignCon2018視察報告

米国 DesignCon2018視察報告

- DesignCon

2018年1月30日(火)~2月1日(木)、アメリカ、カリフォルニア州、サンタクララのコンベンションセンター(図1)でDesignCon 2018が開催されました。

図1. コンベンションセンター

DesignConは、高速コミュニケーションと半導体コミュニティから5,000人の専門家が集まる LSI、パッケージ、システムの製品展示会を併設した電気設計に関する論文の発表会で、3日間で各参加者が技術を披露しあうことでエンジニアの教育のために行われており、今回は、委員会により厳選された90人のテクニカルセッションが組まれています。3日間のイベントプログラムおよび初日のセッションは、図2の通りです。

初日の1月30日(火)は、ブートキャンプとチュートリアルの主に2つに分かれており、前者のブートキャンプは高速信号系のハイスピードと実用的な信号品質の2つのセッションと測定技術の1つのセッションから構成されており、それぞれの基礎を身に着けるプログラムとなっていました。後者のチュートリアルも教育の手法の一つですが、こちらは最先端の技術をセミナー形式で発表されており、特に、高速信号の112Gbpsおよび56GbのPAM4は聴講者も多く、また、今回の出展社の方から伺った感触でも、今回のDesignCon2018の中心的内容の模様でした。

なお、PAM(Pulse Amplitude Modulation=パルス振幅変調)4は、0,1,2,3の4値のデータを使って伝送する方法であり、周波数の4倍のデータを伝送する事ができます。また、チュートリアルには低電圧の技術も説明されており、こちらは今後IoTが進むにつれ、将来的には人は50個程度のIoT製品を身に着ける様になり、その際にはそれぞれに電気を蓄えておく、または充電が必要になるが、もはや困難との見通しで、電気のリサイクルまたは生成のシステムを検討されている物でした。

具体的には、人の動きで発電するデバイス(要は自家発電)で、一部、床などに組み込んで人が歩くと、その動きで発電されるものであるが、消費電力が少ないデバイスの開発も必要であり、まだまだ実用化には程遠い感じでした。

総じて、初日のブートキャンプとチュートリアルについては、まったくの初心者には基礎的な事項が学べるブートキャンプを、最先端で注目されている技術の概要を学びたい場合は、チュートリアルがお勧めですが、いずれもboot(起動)やtutorial(集中的に教える)という言葉の通り、教育の意味合いが強い内容でした。

- テクニカルセッション初日

2日目の1月31日(水)は、2日間開催されるテクニカルセッションの初日でした。会期中用意されている約90のセッションの内、半分強に当たる47の論文発表のセッションと、スポンサーによる約25のセッションが用意されていました(図3)。

前者の論文発表は、大別すると、112Gbpsを最高スペックとした基幹系およびデータセンター用の高速信号関係および関連材料特性の評価、EMIおよびPIに関する論文発表(ただし、EMIおよびPIも高速信号のノイズ低減が中心。)、DDRを中心とした高速メモリ関係で最新技術はGDDR6への取組を説明した論文、の3つに分けることができます。聴講者が多いのは、本イベントの主である高速信号関係で、今回が112GbpsのPAM4が本格的に研究成果が出かけたことも有り、注目されていました。

また、午前と午後の間に、「KEYNOTE」というセッションが有り、ここで「Best Paper Award 2017」にて表彰式が有りました。Best Paper Award 2017は昨年の本会の論文発表で優秀なものが選ばれており、7発表程度が表彰されていました。全て米国の企業が表彰されていましたが、対象者は日系の方や中華系の方もおられました。本年の論文発表が来年表彰されるという流れのため、かなり長いスパンで取組や運営されている事がうかがえます。なお、来年のDesignCon会期は2019年の1月29日~31日までの3日間となります。

本日の発表で特筆すべきセッションは、「Fiber weave effect: Modeling, measurements, challenges and its impact on differential insertion loss for weak and strong-coupled differential transmission lines.」・・・①、と「A Causal Conductor Roughness Model and its Effect on Transmission Line Characteristics」・・・②、と「Designing DC-Blocking Capacitor Transitions to Enable 56Gbps NRZ & 112Gbps PAM4」・・・③でした。

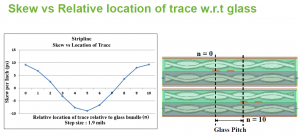

①はガラス繊維と導体の重なりによるスキューを考慮した設計手法で、ガラスクロスリッチの場所に配線されている信号と樹脂リッチの場所に配線されている信号とは、1インチ(=25.4mm)あたり、18ps程度スキューが異なるとの報告(図4)で、このスキューを取り入れた設計、シミュレーション技術が紹介されていました。

図4. ガラスクロスにょるスキューの影響

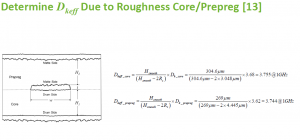

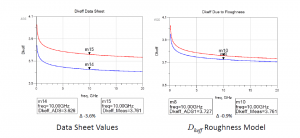

②は導体である銅箔表面粗さを考慮したシミュレーションモデリング手法で、銅箔表面粗さを考慮しないデータシートによるモデリングの場合、シミュレーションと実測の実効誘電率に大きな差がありますが、表面粗さを考慮した場合、シミュレーションと実測の相関性がかなりよくなるというものでした(図5)。

図5. 銅箔表面粗さの実効誘電率の影響

③は56G/112GをターゲットとしたAC結合コンデンサの実装設計手法の論文発表であり、コンデンサのフットプリントのサイズ1つをとっても、反射特性(S11)に差がみられるとの結果でした。上記の3つは、いずれも超高速対応のための詳細な設計手法でシミュレーションが中心の内容でした。

一方で、展示会も同日の午後から開催されており、約180社(図6)の出展が有りました。展示会の規模としては、このシリコンバレーのエリアでは平均的クラスとの事ですが、展示内容はかなりデータセンター向けなどの高速信号を意識したものが多くありました。

- 展示会

出展社の業種しては、材料メーカ、コネクタ・ケーブルメーカ、基板メーカ、測定機器メーカ、シミュレーションツールメーカが主で、日本の電気の展示会で一般的な、半導体や部品メーカの出展はほぼ見られませんでした。展示物でよくみられる内容として、測定のデモを行っているブースも有るのですが、日本でおなじみの半導体メーカが行っているのではなく、本展示会ではコネクタメーカが主に行っていたのが印象的でした(当然、計測器メーカはデモを行っていました。)。なお、会場の雰囲気は図7の通りで、コンパニオンなどは不在で、展示自体には派手さも無く、かなりエンジニア寄りの内容となっています。

図7. 展示会場

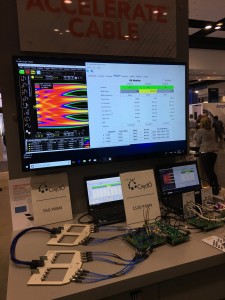

その中で、Samtecのブースでも112GbpsのPAM4の展示が有りましたので、紹介します(図8)。こちらでの112Gbps伝送は、SerDesから出力した112Gbps(PAM4)の信号を、AcceleRate® Cableを経由して、もう片方の受信ICで受けた波形をデモ展示していました。また、56Gbps(PAM4)については、バックプレーンを経由した波形のデモを行っていました。56Gbpsや112Gbpsになってくると、バックプレーンにプリント基板を使う事は伝送ロスの関係からかなり厳しいとの事で、バックプレーンボードの代りに同社のケーブルとコネクタを使っていました。ケーブルに変える事により、プリント基板を使う場合に比べて、伝送特性が改善されて、リタイマーチップなどを使わずにすみシステムコストの低減がはかれるとの事です。

図8. Samtecブース 112Gbp PAM4

また、リタイマーチップを使用する必要性が無い事から消費電力を削減することも可能になって来るようです。なお、プリント基板で112Gbpsで1mの伝送を行う事は非常に難しいとの事ですが、逆に言うと、従来のコストと同程度で実現できるとかなり有効だという事になります。

その他の出展会社もターゲットはかなり似たような所に有り、通信機器メーカであるCISCOを意識した展示会である事がうかがえます。また、基板メーカである当社からすると、通信機器に強い、サンミナ、京セラ、と言ったところが、データセンター向けを意識したかなり大きく厚い基板やバックプレーンボードを展示していました(図9)。

図9. SANMINAブース

一方で、本日のプログラムおよび展示会終了後、Samtecさんのご厚意で「Meet&Geekイベント」というものにお招きいただきましたので、写真(図10)を合わせてご紹介させていただきます。

図10. Samtec Meet&Geekイベント

- テクニカルセッション2日目

3日目の2月1日(木)は、2日間開催されるテクニカルセッションおよび本DesignConの最終日でした。残りの論文45個程度が発表されていました(図11)。

本日の発表で特筆すべきセッションは、「Effective Link Equalizations using FIR, CTLE, FFE, DFE, and FEC for Serial Links at 112 Gbps and Beyond」・・・④、と「Equalization Requirements for DDR5」・・・⑤、と「An Efficiently-Generated Via Model For PCB Crosstalk and Link Analysis」・・・⑥でした。

④は112G対応のためのデバイスの波形補正技術やエラー補正回路について、⑤はDDR5対応のためのイコライザ技術(DFE)について、⑥は56G/112Gのクロストーク対応のためのViaのモデリングについて、等であり、やはり、超高速へ向けたデバイスの機能と詳細なPCB設計手法が中心でした。

- まとめ

以上が2018年1月30日(火)~2月1日(木)の3日間開催されたDesignCon2018の概略です。

総じて、通信機器を中心とし、また論文発表などアカデミックな内容も有り、かなりニッチな業界向けにも関わらず、たくさんの方が来場されていました。通信機器をターゲットにした展示会であるため、米国の電気業界の最新事情を本イベントが網羅をしている訳ではありませんが、データセンターを中心とした通信業界に属する会社またはその業界への販売を目指している会社が情報を得るためには有意義なイベントでは無かったのでは無いかと思われます。一方で、産業機器向けの電気関係のイベントはシカゴを中心とした展示会が担っているとの事で、視察できる機会が有ればご報告したく思います。

追伸:筆者は翌日の2月2日(金)に開催された「IBIS summit」にも参加をしております。本紙で書ききれなかったDesignCon2018の詳細とIBIS summitは次の機会にご報告致します。また、詳細をお聞きになりたい方、または、本件の類似事項を実現したい方は、こちらまたは営業担当までお問い合わせをお願いします。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。