プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 事例紹介 > 高速DRAMの同時動作シミュレーション方法

高速DRAMの同時動作シミュレーション方法

課題

高速DRAM伝送において高精度な同時動作解析とデザインレビューの効率化を実現したい

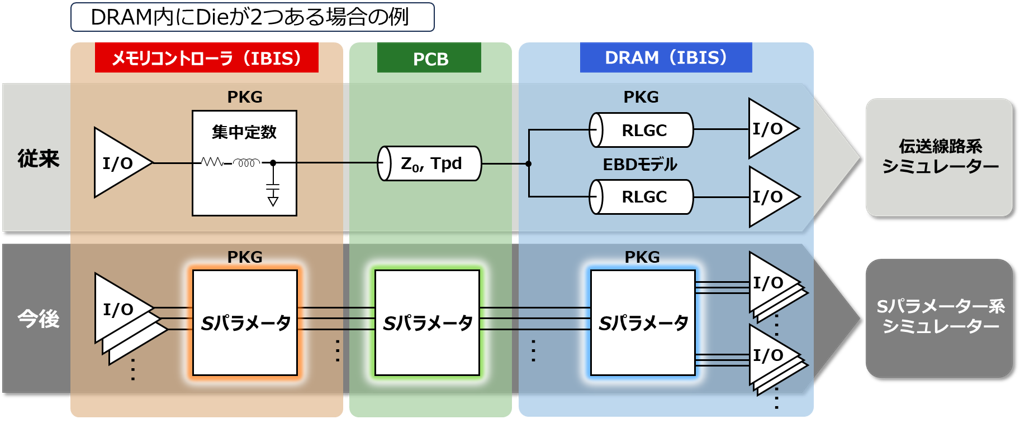

DDR4やLPDDR4等の高速DRAMを搭載するプリント基板では、設計段階にシミュレーション検証を行うことが一般的である。この信号品質(SI)検証の方法を図1に示す。

従来、デバイスのパッケージのモデルは集中定数、プリント基板は伝送線路が用いられてきたが、高精度化のためSパラメータを用いた同時動作シミュレーションが求められている。この場合、シミュレーション工数の増加による設計期間の長期化に加え、結果が煩雑になることでデザインレビューの判断材料として扱い難いという課題がある。

当社のご提案

この課題を解決するため、弊社では、キーサイト・テクノロジー社 ADS Memory Designerを用いたSパラメータ系同時動作シミュレーションと、JEDEC規格に準拠したレポートの提供をおこなっており、その事例を紹介する。

- 1. 方法

-

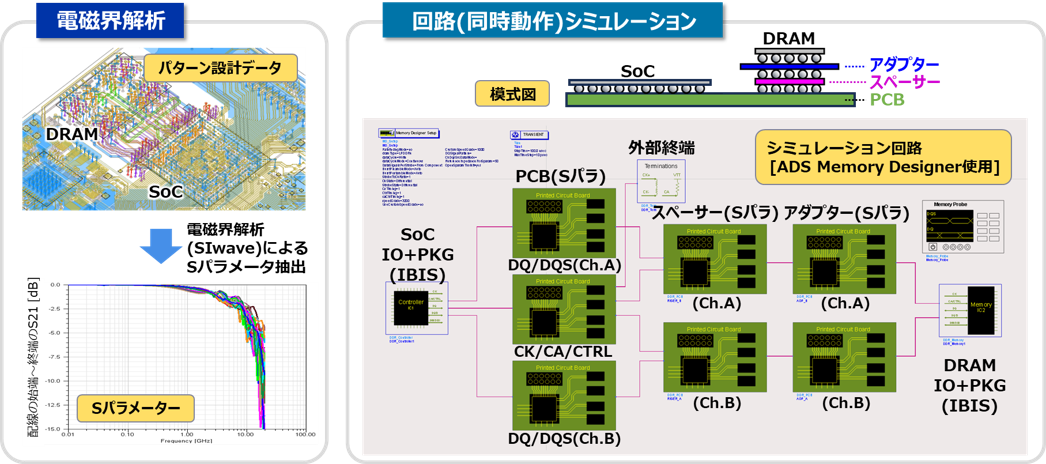

プリント基板上でメモリコントローラ(SoC)とLPDDR4-SDRAM(x32)が1対1で接続されたを事例を紹介する。図2にシミュレーション方法の概要を示す。

図1 信号品質(SI)検証の方法

まず、ANSYS社 電磁界解析ソフト(SIwave)にパターン設計データを取り込みSパラメータを抽出する。つぎに、回路シミュレータ(ADS Memory Designer)にて、デバイスモデル(IBIS)とSパラメータを統合する。この事例では、波形実測に用いる観測用のアダプター基板とスペーサー基板のSパラメータを含んでいる。ここで、ADS Memory Designerは高速DRAMの信号品質(SI)検証に特化したGUIであり、IBISとSパラメータのすべての信号を容易に接続することが可能であり、短時間でのシミュレーション・セットアップを実現できる。また、電磁界解析に関する当社ノウハウにより、Sパラメータの抽出方法を最適化することで、信号波形シミュレーションの精度、解析時間の短縮を実現している。

- 2. 結果

-

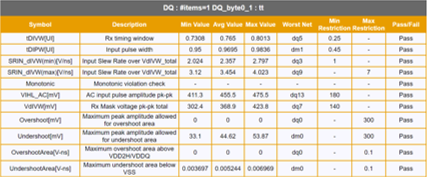

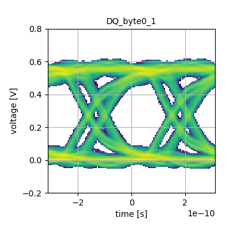

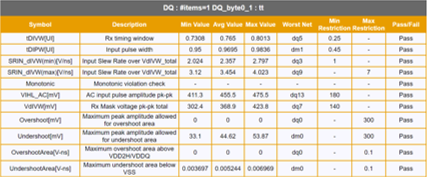

Ch.Aに関するシミュレーション結果として、DQレポートの例を図3に示す。

(a) 概要

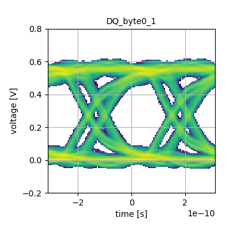

(b) 詳細1 全波形重ね書き

(b) 詳細2 タイミング

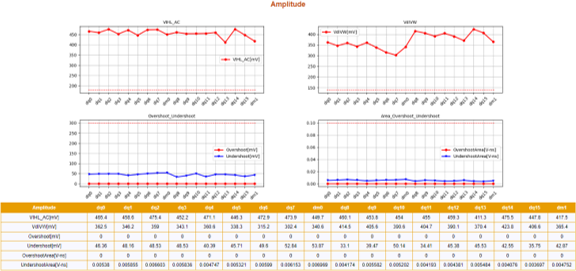

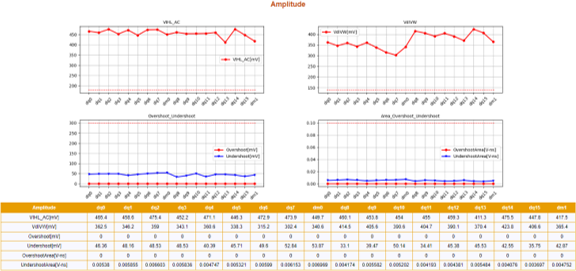

(b) 詳細3 振幅

(b) 詳細4 アイダイアグラム

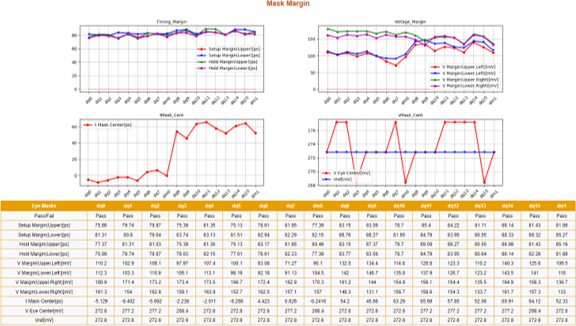

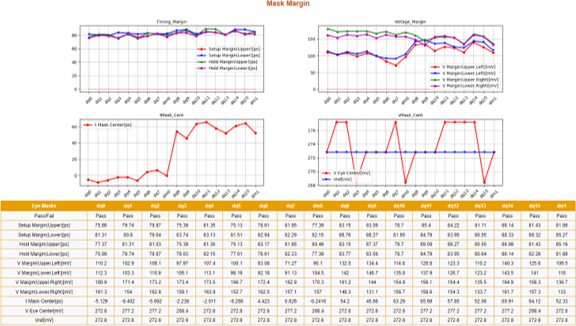

(b) 詳細5 マスクマージン

図3 Ch.A DQシミュレーション結果のレポート例

(a) 概要

(b) 詳細1 全波形重ね書き

(b) 詳細2 タイミング

(b) 詳細3 振幅

(b) 詳細4 アイダイアグラム

(b) 詳細5 マスクマージン

図3 Ch.A DQシミュレーション結果のレポート例

レポート内容は概要と詳細に分かれており、概要ではJEDEC項目に対する合否判定を確認する。ここで、ワースト信号を同定することができるため、規格不適合やマージンが少ない場合、直ぐにパターン修正を実施する。詳細では、①全波形重ね書き、②タイミング、③振幅、④各波形、⑤マスクマージンを確認する。すべての信号波形を定性評価、かつ、各JEDECパラメータを定量評価することで、パターン設計段階のデザインレビューの判断材料として有効活用できる。

結果

高速DRAMの高精度な同時動作シミュレーションを実現

電磁界解析によるSパラメータ抽出とADS Memory Designerを用いた同時動作シミュレーションにより高精度な信号品質(SI)検証を実施可能です。DDR4/LPDDR4に関しては、JEDEC規格に対応した専用レポートを提供し、パターン設計段階でのデザインレビューの判断材料に活用頂けます。

これら検証結果に関する詳細資料や関連資料をご要望の方は、以下ダウンロードページより会員登録を行っていただきますようお願い申し上げます。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。