組込み機器向け高速伝送ボード開発セミナー〜最新高速DRAM(LPDDR5、DDR5)、最新FPGA搭載の実例〜

【イベント概要】

2025年7月4日大阪(グランキューブ大阪(大阪府立国際会議場))、7月11日名古屋(ウインクあいち 愛知県産業労働センター)、7月16日東京(秋葉原UDX)でプライベートセミナーを現地開催にて実施しました。

本セミナーイベントは、アルテラ合同会社、キーサイト・テクノロジー株式会社に講演協力を頂き、最新FPGAと高速DRAM(DDR5・LPDDR5)のボード開発に関し、設計のポイントやシミュレーション、波形評価について、4つの講演セッションと関連商品の展示を行いました。

150名程のお客様がご来場くださり、各セッション後は講師に直接質問を頂き、活気溢れるイベントとなりました。

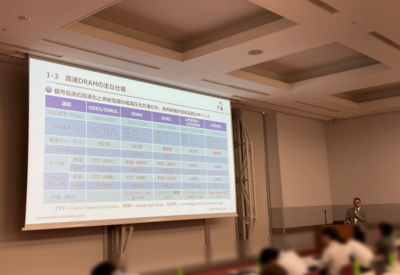

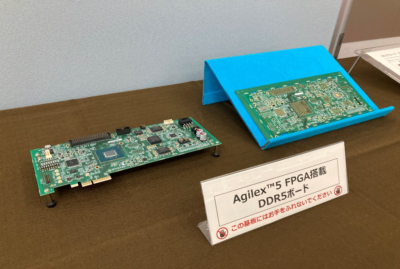

【セッション1「LPDDR5, DDR5搭載基板の開発方法と実例」】

セッション1では、当社が開発したAgilex™ 5EとDDR5, LPDDR5搭載ボードを題材とし、波形シミュレーションによるODT検討方法を解説しました。また、DDR5, LPDDR5から電源インピーダンスに規定値が設けられており、電源シミュレーションにより、その結果も紹介しました。

あと、プローブアダプターを介在させたDDR5 SO-DIMMの実測事例を紹介しました。

【セッション2 「AgilexファミリーデバイスにおけるLPDDR5、LPDDR4メモリを使用する際の設計ポイント」】

セッション2では、アルテラ合同会社にAltera FPGAのラインナップをご紹介頂き、Agilex™ 7 M-SeriesとDDR5 やAgilex™ 5 E-SeriesとLPDDR4の設計事例を解説頂きました。Quartusを用いたコントローラの設定方法からシミュレーションを含む実機開発方法などが学べました。

【セッション3「DDR5メモリの波形品質測定の実際」】

セッション3では、キーサイト・テクノロジー株式会社にUXRシリーズオシロスコープを用いて、DDR5 SO-DIMMにBGA Interposerを搭載した波形測定についてご紹介頂きました。各種信号は波形取得やアイパターン描画方法、InfiniiSim機能による観測点移動とDeEmbeddingの効果、イコライザ機能による波形補正、自動測定ソフトウェアなど、評価手法が学べました。

【セッション4「高速DRAM搭載基板の波形シミュレーション高精度化」】

セッション4では、より高速化していく高速DRAMに対し、電磁界解析にてプリント基板を高精度に解析したSパラメータを用いた同時動作シミュレーションにより、リファレンスプレーンの欠損やクロストークを考慮した波形解析ができることを解説しました。また、半導体の電源電圧変動を考慮した波形解析(Power Aware解析)についても解説し、半導体のPDNモデルが解析精度に大きな影響を与えることを紹介しました。

【まとめ】

今後、DDR5・LPDDR5の採用を検討されている開発者様を対象として、アルテラ合同会社、キーサイト・テクノロジー株式会社に講演協力を頂き、最新FPGA、波形評価・シミュレーション手法について、対面形式のセミナーイベントを実施しました。多くのお客様にご来場いただき、関連商品の展示コーナーにて直接講師にご質問いただき、大盛況なイベントとなりました。

今後も、お客様にとって有意義なイベントを計画したいと思いますので、ご要望がございましたら、営業担当までご連絡をお願いします。

【セミナー資料】

セッション1「LPDDR5, DDR5搭載基板の開発方法と実例」

https://www.ritael.co.jp/mypage/document/2025-07-17-01/

セッション4「高速DRAM搭載基板の波形シミュレーション高精度化」

https://www.ritael.co.jp/mypage/document/2025-07-17-02/

関連する資料

LPDDR5、DDR5搭載基板の開発方法と実例

2025年7月4日、7月11日、7月16日のRITAエレクトロニクス主催プライベートセミナーにおける弊社講演資料です。

2025.07.17

イベント開催報告